安博娱乐平台首页

安博娱乐平台首页时间: 2024-06-08 19:47:27 | 作者: 黑色网格防静电胶带

有了ESD,迅速让静电导到PCB板的主GND上,可以消除一定能力的静电。

2、系统地与机壳地分离的电子科技类产品,内部电路也不会设计成与机壳连通,所以干扰进入内部电路主要是耦合方式。通过耦合方式进入电子科技类产品内部的情况,与机壳上建立的dv/dt,接地线上建立的di/dt有关,与机壳上建立的电压绝对值不直接相关。这也是大机箱的电子设备不易受干扰干扰的原因,对地电容比较大,不易建立较大的dV/dt和di/dt。

3、如果耦合是干扰的主要路径,我们大家可以采取一些措施,措施可以是很多不同的方法。一般来说耦合路径会比较多,有一些还不易察觉,直接采取阻断耦合路径的方法不易实现,除非通过结构分析、干扰分析发现了明确的结构问题或者路径。拉开距离能减小耦合电容,间隙衬垫聚四氟乙烯等材料也能减小电容,由此减少耦合强度。

B.一根高阻抗的输入线与一根本来没有干扰的导线捆扎走线,而这个根本就没有干扰的导线有一段比较靠近机壳,这也会有耦合ESD的问题。

4、或多或少总有一部分干扰经耦合进入内部电路,是否能处理好这些耦合进来的干扰;系统接地是关键。

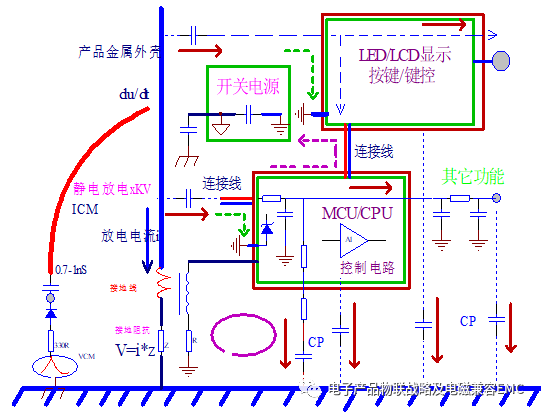

连续的、靠得住的系统接地,可以承载内部电路不受外部干扰,不管系统地是否实际接大地。参考上图中的耦合路径分析箭头路径分析。

在我进行ESD的内部结构电路的PCB分析时,我们大家可以看到在IO线端口见到电阻电容的设计,这些电容可以把耦合过来的干扰导入系统地。

注意:对于高频电路,电容对干扰和有用信号同时起作用,所以不能用于高频信号电路。但使用TVS器件时(较小的结电容)电压高于信号电压,基本对有用信号没有影响。

有必要说明一下:当信号电平为0时,从0电平开始干扰信号就需要消耗能量给电容充电,适当电容量能吸收掉干扰能量,使干扰电平达不到逻辑动作电平,电子科技类产品电路不受干扰。TVS在这样的一个过程中基本不起作用,即便干扰电平已达到逻辑动作电平。

很多时候由于干扰能量是吸收不完会穿过PCB,会通过CPUMCU,如上图中的箭头所示路径!

所以后面我再分析电子科技类产品内部ESD的问题设计时知道:一方面我们要规划干扰在PCB上的路径(注意这是在布板PCB板时需要提前规划);另一方面要尽量控制干扰幅度。

5、空气放电主要是空间的辐射成分,已没明确的路径,对于容性耦合情况,受扰部位会有较大面积和较近的距离,不太容易识别路径,所以从敏感部位入手比较容易。

实际的ESD都是非常高电压的空气放电模式,空间放电于接缝、插座、按键等;

在对金属壳体做接触放电通过的前提下,需要对这些缝隙做空气放电,也许会出现干扰情况如:显示闪烁、误读按键、机器重启复位等。

我们要首先排除放电火花立即进入电子科技类产品或设备的情况,干扰过程相对简单,我们大家可以寻找一下放电怎么会绕过壳体!

接触放电于金属壳体,产生比较大的di/dt,在结构件接地良好的情况下,仅有微弱的dv/dt。空气放电于金属壳体,枪头有较大dv/dt,枪前部高压部分体积越大,这个dv/dt越强;这个dv/dt很可能超过接触放电在接地不良金属构件上产生的大的电压V;

同时火花有较大的di/dt,也就是说有突变电场与磁场。突变电场以近场容性耦合的方式从绝缘构件部位耦合到内部电路,突变磁场以近场感性耦合方式穿透绝缘件进入内部电路。

1、外壳和结构件:金属以及可导电的电镀材料等,属于容易吸引和聚集静电的材料;ESD要求很高的项目要尽可能避开使用这些材料。

2、必须使用导体材料时:结构上要事先预留有效而布局均匀的接地点;一般来说,顶针或者金属弹片的接地效果优于导电泡棉和导电布。

4、外壳上的金属件,距离器件和走线、堆叠上避免器件于孔、缝边;如果没办法避免的话,则要在组装上想办法堵;常见的做法有粘贴高温胶带或者防静电胶带等阻隔;所有结构设计需要留有增加隔离片的空间。

本帖最后由 gk320830 于 2015-3-7 19:50 编辑 LED恒流驱动电路的设

)对电子设备的干扰和破坏,需要采取多种技术方法进行防范。从分层、恰当的布局布线和安装等方面介绍了PCB中的抗

的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(

工作。其实,这些可靠性工作,目的解决产品可靠性工程问题,严控和降低产品质量风险。最近,看到有一个可靠性设

2.3 总体设计2.4 软硬件设计2.4.1 硬件设计2.4.2 软件设计2.5 方案论证

复位或死机,走线时注意加地线屏蔽,电路也应该做适当处理。 信号线路上有选择的添加一些合适的电容或串联合适的电阻,有助于提高

负载率在50%以下的时间占全部运行时间的50%以上,满负荷的机会不多,若采用普通常规的控制

的讨论采用MSI、LSI及VLSI通用的74系列集成芯片设计各种常用的组合逻

的作用:可以通过话务统计来观察一个整体网络性能的中等水准可以通过话务统计来发现网络中的故障问题可以通过话务统计来对网络性能进行优化线

其本质,利用数据仓库技术进行开发和实现,并阐述了如何利用数据仓库技术从需求

12.3 TA两片机集成电路简介公共通道公共通道指图像信号和伴音信号共同经过的电路,

在电子产品设计中,可制造性设计是生产的基本工艺质量的保证,并有助于提高生产效率,产品的可

手机、数码相机、MP3播放器和PDA等手持设备的设计工程师,正不断地面临着在降低整个

研究 交流电经过二极管整流之后,方向单一了,但是大小(电流强度)还是处在不断地变化之中。这种脉动直流一般是不能直接

方案 工程设计模拟软件与服务的全球领先供应商 MSC.Software 今天宣布,中航起落架有限责任公司 (LAMC) 选择了其工程设

随着全世界汽车电子产业的兴起和人们对汽车安全的信息化、智能化的不断追求,汽车胎压监测

随着国内近期电视台/剧场的新建及改建大型项目的频繁发生,利用网络的强大功能引进先进的管理技术,合理

本文论述利用印制电路板(PCB)工艺技术制造的无磁心 变压器 的基本结构及形式,设

及其在功率驱动电路中的应用。实验证实了在高频工作时,无磁心 PCB 变压器

的技巧程序语句参数的设置输出结果的判读等并应用Pspice 对实例电路进行特性仿线

基于.NET开发平台,以Oracle为后台数据库,采用B/S结构模式,分为数据导入

本文档的主要内容详细的介绍的是使用OrCAD PSpice实现放大电路的设

耐性测试方法依据产生静电的模型,分为以下三种:①HBM、②MM、③CDM。 其中

23+项常见设计问题,解决设计隐患 3.智能拼版,节约单板采购成本 4.智能阻抗计算和反算 5. BOM智能

23+项常见设计问题,解决设计隐患 3.智能拼版,节约单板采购成本 4.智能阻抗计算和反算 5. BOM智能

23+项常见设计问题,解决设计隐患 3.智能拼版,节约单板采购成本 4.智能阻抗计算和反算 5. BOM智能

电子发烧友网站提供《Vivado Design Suite用户指南:设

问题排查中,最重要最难的无疑是静电路径问题了。 本次就和大伙稍微探讨下

,哪怕在为大家排查静电问题的时候提供一丝丝有益的思路,我就觉得没有白写。